論文

# スケーラブルなセルライブラリを用いたLSI試作のデザインフ ロー設計試行(ON SEMI 1.2μm)

樋口 拓哉\*1 大金 淳一郎\*1 清水 尚彦\*2

## Building A Design Flow for ON SEMI 1.2μm Digital LSI with A Scalable Cell Library

by

## Takuya HIGUCHI, Jun'ichiro OGANE and Naohiko SHIMIZU

(received on May 8, 2010 & accepted on September 21, 2010)

#### Abstract

We have built design method for submicron LSI with three or more metal layers those utilize a scalable cell library within Alliance VLSI CAD System. We confirmed that there were no design rule errors for our Rohm  $0.35\mu m$  and  $0.18\mu m$  digital LSI TEGs with our method. In this paper, we try to build a new method for ON SEMI  $1.2 \mu m$  digital LSI which has only two metal layers with the same scalable cell library. The chip is on the way of fabrication.

Keywords: LSI design, Alliance VLSI CAD System, VDEC, Design flow, ON Semiconductor(1.2μm)

#### 1. はじめに

LSI 設計は最終的にチップ製造のためのデザインルールに従う マスクパターンを作成する作業である。デザインルールは製造 プロセス毎に異なるので、通常、プロセス毎にデジタル回路の基 本回路パターンであるセルの一群(以下セルライブラリ)を作成 する、論理回路の基本素子となるセルの設計によって、LSI の性 能が大きく左右されるため、セルの設計は熟練した技術者によっ て細心の注意の元に行われる。さらに、各セルは、消費電力、遅 延時間、負荷特性、回路シミュレーションモデルの検証を十分 行い、EDA ツールへのライブラリとして登録可能な形にまとめ る。プロセス毎に発生するこの大きな設計負担を低減するため、 我々は異なるプロセスでもスケーラブルに対応可能なセルライ ブラリを有する EDA ツール Alliance によるチップ試作を行って きた。この手法ではセルライブラリにおけるセグメントの長さ。 幅をチューニングパラメータにより調整するルールファイルを 作成し、スケーリングによりレイアウトの最適化を行う。しか し、Alliance の基本設計が行われた時期と、現在の LSI プロセ スではデザインルール自体が大きく変わりつつあり、ツールに まかせたスケーリングではデザインルールエラーが多数発生す る。そこで我々は、過去、Rohm 0.35μm, 0.18μm プロセスを用 いて、実際に LSI 設計を行い、デザインルールエラーのないレ イアウト作成のための手法を研究してきた。577 これらの研究成 果により、サブミクロン、ディープサブミクロンプロセスにおけ る Alliance の問題点が明らかにされてきたが、個々のプロセス ごとにライブラリに変更を加える必要が生じるとスケーラブル ライブラリの価値が低減する。また、Alliance ではライブラリ以 外に、プログラム中にデザインルールを仮定して配置配線処理を 行っているため、ライブラリ自体がスケーラブルになっても配 置配線でエラーが発生する場合があった。我々は、従来、配置配 線ツールが生成するエラーは、最小プロセスピッチを拡大する ことで対応していたが、若干の LSI レイアウトの拡大を招きあ まり好ましい対策ではない。そこで、これらの問題点を整理し て、今後の対策を検討する必要があった。今回、従来行ってきた デーブサブミクロンプロセスである Rohm 0.35μm, 0.18 μm に 加え、サブミクロンプロセス、ON SEMI 1.2μm の試作を行い、 デザインフローの確立をした。過去のディープサブミクロンプ ロセスと異なり、ON SEMI 1.2μm では配線に用いるアルミ層が 2層となっているため、これまでとは異なる配線方法を取った。 手法の変更に伴い発生した新たな問題点の分析を行う。Table 1 に各プロセスの概要を示す。また我々は、座学のみでなく、もの づくりを通して LSI 設計を学ぶことを目的とし、VDEC を利用 したチップ試作を試みている。VDEC には設計を行うための各 種 EDA ツール、デザインフローが用意されているが、技術者と しての将来を見据え、LSI 設計フロー自体を見直し、作りあげる 力を養うため、オープンソース EDA ツールを用いた新たな設計 フローの確立をもう一つの目的とする。本稿では VDEC チップ 試作を通して得られた知見を述べる。

## デジタル LSI 設計

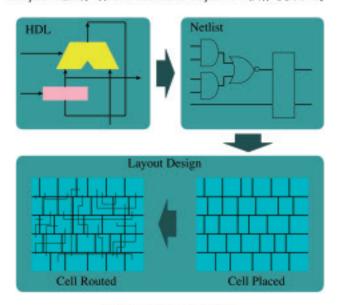

HDL からの一速のデジタル LSI デザインフローを Fig. 1 に示す. HDL の論理合成により得られたネットリストの持つセル情報、およびセル間の接続情報に基づき、セルの配置、配線を行う、

## 3. VDEC チップ試作概要

東京大学大規模集積システムセンター (VDEC) は、教育および学術研究目的に限って、商用ツールをアカデミックライセンスとして無償利用可能とするチップ試作環境を提供している。

<sup>\*1</sup> 工学研究科 情報通信制御システム工学専攻 1 年

<sup>-</sup> 情報通信学部組込みソフトウェア工学科 教授

<sup>2)</sup> 我々は、VDEC が提供したプロセスのうち、Rohm 0.35µm、0.18µm に加え、新たに ON SEMI 1.2µm での試作を試みた。

Fig. 1 Digital LSI design flow

VDEC はチップ製造において、大手 EDA ベンダーの Cadence Design Systems, もしくは Mentor Graphics 社のツールによって デザインルールチェックが通っていることをテープアウトの条件とする.

## 4. OSS EDA Alliance 概要

#### 4.1 Alliance VLSI CAD System

LSI レイアウト設計にはフランスの Pierre et Marie Curie University にて開発されたオープンソース EDA ツール, Alliance VLSI CAD System(以下 Alliance) を使用した。Alliance はセルベース方式で LSI を設計するが、備えられたセルライブラリは欧州の CMP, Euro Practice での 1.0µm チップ試作を前堤に作られており、本来は VDEC でのチップ試作には対応していないが、入ルールペースのセルライブラリを各種プロセスルールに適合させるという手段を持つ。そこで、デザインルールに適合させるためのレイアウトを決定するルールファイルを記述し、必要に応じライブラリの修正を行った。

## 4.2 Allilance の特徴

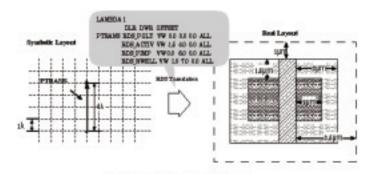

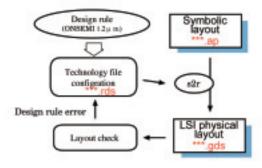

Alliance はスケーラブルなセルライブラリを持つ、仮想配置 (symboric layout) で配置配線を行った後、s2r(symboric layout to

Table 1 Processes summary

| Process       | Metal | Poly | Gate(pm) |

|---------------|-------|------|----------|

| Roben 0.35µm  | 3     | 2    | 0.35     |

| Rohm 0.18µm   | 5     | 1    | 0.18     |

| ON SEMI 1.2µm | 2     | 2    | 1.2      |

real layout) で実配置に変換し、ファウンドリのデザインルール に適合したチップ製作可能なレイアウトデータとする。(Fig. 2 参照)

- 仮想配置… 輪の長さ、座標情報のみのセルライブラリを配置、配線した状態。

- 実配置… ルールファイル (テクノロジファイル) に従い、ファウンドリに提出できるレイアウトデータを生成した状態。

変換は、ユーザが記述したルールファイルの記述に従い行われる、この手法により、プロセスルール毎に固有のスタンダードセ ルライブラリを必要としない設計が可能である。

ルールファイルは λ(ラムダ) を基準値とする、Alliance で意味 する λ とは、通常のゲート幅ではなく、仮想配置で用いる座標 1 コマの値であり、ゲート幅は独立して宣言する。通常の λ ベー ス設計と異なり、Alliance では、λ ベースで構成されたセグメン トの長さと幅をルールファイルによって修正し、個別プロセスへ の最適化が可能である。しかし、標準のライブラリは 1.0μm の プロセスでの λ ルールを前提とするので、VDEC の提供プロセ スに適合させる上で後述の問題があった。

Fig. 2 Symbolic and real layouts

#### 5. 本手法による適去の試作

本研究室では、これまでにディーブサブミクロンプロセス、 0.35µm、0.18µm プロセスの LSI 設計を、Alliance によるスケー ラブルなスタンダードセルライブラリを用いて行った。5% これ らの試作では、各チップ毎に I/O バッドを VDEC の仕様に合わ せて独自開発した。また、Alliance が前堤とするラムダルールで は対応しきれないルール、RC 遅延によるクロックのスキュー問 題等が生じる事が判明した。7% 試作を進める上でこれらを対処 した。

## 5.1 ディープサブミクロンプロセス設計時の問題点

#### 5.1.1 デザインルール

Alliance のセルライブラリは、スケーラブルなラムダルール によって仮想的に記述される。実際のデザインルールをラムダ ルールのみに適合させると不必要に大きなチップとなるため、ラ ムダルールのレイアウトの各サイズをパラメータ (RDS) により 増減し、最適設計を行う仕組が導入されている。配置。配線プロ グラムも同じラムダルールを採用し、RDS パラメータによりレ イアウトを調整する。しかし、ディープサブミクロンプロセスで は、1.0μm 向けに作成されたラムダルールでは対応しきれない ルールがあったため、仮想配置自体の変更(セルライブラリ変更) が必要となる。一方、配置。配線プログラムが前提とするラムダ ルールは、パラメータ化されておらず、この調整不良を原因とす るエラーが発生した。

#### 5.1.2 クロックスキュー

Alliance をはじめとした、多くのオープンソース EDA ツール にはクロック信号が考慮されていないものが多い。ディーブサ ブミクロンプロセスにおいて、Alliance のクロックのルーティン グ機能ではスキューが大きくなることが考えられる。そのため、 高速なデジタルシステム設計を目的とした、クロック分配網の工 夫によるスキュー低減を考察した。

#### 5.2 対策

#### 5.2.1 ライブラリの修正

セルライブラリは、ディーブサブミクロンのルールに合わせて 修正した、レイアウトエラーを解決し、最終的にデザインルール チェッカを用いてデザインルールエラーが0個になる事を確認 した。

#### 5.2.2 低スキュークロック自動配線ツールの実装

Alliance のスキューを考慮しないルーティングへの対策として、メッシュ型クロックの自動生成ツールを Alliance ツールチェインの一部として利用可能な形で実装を行った。メッシュ型クロックは、H-クロックツリーに比べ、Alliance への実装が容易であり、また、セルライブラリを解析した結果、それぞれのセルに対しメッシュを張る方法で、チップ面積、配線率等のコストをかけずに設計が可能であった。

## 6. 本論文の ON SEMI 1.2μm プロセスチップ試作

オンセミ 1.2μm ではラムダルール変更は不要と考えられ、バ ラメータ調整のみの試作が可能となる事を期待して試作申し込 みを行った。

#### 6.1 ディープサブミクロンとの相違点

ディープサブミクロンプロセスは、配線は3層以上使用可能 であった。しかし、オンセミ1.2μm プロセスは、アルミ2層で ある。ディープサブミクロンプロセス設計に使用したデザイン フローにおける自動配線は、セルオーバルーティングであり、2 層配線に対応しない。そのため、配線領域をセル領域外に確保す る Alliance Ver.4 を使用することにした。

#### 6.2 設計プロセス

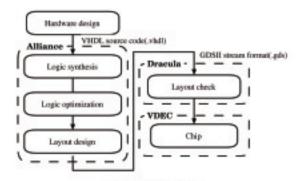

オンセミ 1.2μm プロセスをチップ試作する上で、ハードウェ ア記述から最終的に VDEC で試作可能なレイアウトデータを作 成するまでのデザインフローを作成し、それを試行した。

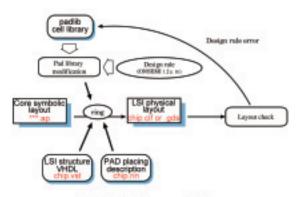

実際に試行したデザインフローを Fig. 3 に示す。

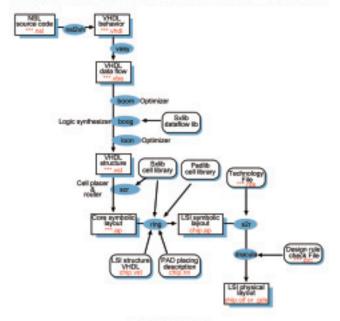

Alliance は、多くの LSI 設計ツールに対する総称であり、今

Fig. 3 Design flow

回は、Table 2 に示すツールを用いて VHDL から論理設計、論 理合成、論理最適化、自動配置配線を行った。ただし、VHDL の記述レベルは低く設計が困難なため、設計言語は NSL<sup>9</sup> と し、nsl2vh で Alliance 用 VHDL を生成した。 NSL から変換し

Fig. 4 Tool flow

た VHDL を、vasy を用いて VHDL ビヘイビア記述へ変換し、 boom, boog, loon を用いて Alliance 付属のスタンダードセルラ イブラリ (sxlib) に対し、論理合成、最適化を行う。その後、scr を用いて配置配線を行い、仮想配置のレイアウトを出力する。設 計した回路の入出力パッドとの接続を記述した VHDL Structure ネットリストと、配置順序指定ファイル (.rin) を作成し、ring を 用いてパッドを含めたレイアウト全体の仮想配置を生成する。

| tool    | function                            |  |

|---------|-------------------------------------|--|

| vasy    | VHDL Compilation                    |  |

| boom    | Optimization of behavior            |  |

| boog    | Logic synthesis                     |  |

| loon    | Optimization of netlist             |  |

| scr     | Placement and routing               |  |

| ring    | Placement and routing for pad ring  |  |

| s2r     | Symbolic to real layout translation |  |

| graal   | Symbolic layout editor              |  |

| dreal   | Real layout editor                  |  |

| dracula | Design rule checker                 |  |

Table 2 Tools

最後に、s2r を用いてテクノロジーファイル (.rds) をもとに、レ イアウトデータ (.gds) を生成する。

設計されたレイアウトデータは、Cadence 社 Dracula を用いて 試作可能か評価する、ツールフローは Fig. 4 の通りである。

## 6.3 日程、作業の内訳

作成した設計プロセスにおいて、必要な作業を洗い出し、テープアウトまでの作業スケジュールを見積もった。その結果、大きく分けてファウンドリ指定の設計規則に適合したレイアウト設計と、組み立てベンダの指定するパッド配置に適合するための、I/O パッドの修正の二つの作業が必要であることが分かった、実際に行った 2010/3/4 からテープアウトまでのスケジュールを Fig. 5 へ示す。

Fig. 5 Schedule

## 6.3.1 レイアウト設計

今回採用した Alliance におけるレイアウトの作成は、スケー ラブルなセルライブラリをテクノロジーファイルに沿って実際 のレイアウトへと変換するものである。そのため、このテクノロ ジーファイルをオンセミ 1.2µm に対応させる事が目的となる。

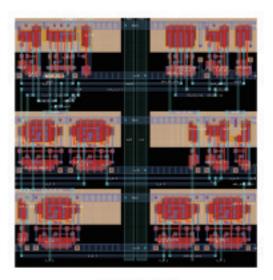

テクノロジーファイル作成作業は、Fig. 6 の工程で行う、オ ンセミ 1.2μm 設計規則をもとに、テクノロジーファイルの各レ イヤの形状を設定する。作成したレイアウトの確認は、dracula で行い、エラーが存在すればテクノロジーファイルを修正する。 スタンダードセルの修正例を Fig. 8(sxlib) に示す、レイヤの凹 みや、微妙な隙間でもレイアウトエラーを発生するため、Fig. 8(sxlib) のように、微妙な隙間を無くすように修正する。Fig. 6 の作業で、全てセルライブラリと配置配線後のレイアウトにおい て、デザインルールエラーを 0 個にする。

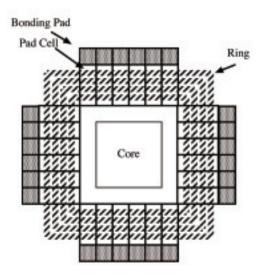

#### 6.3.2 I/O バッド

パッドはチップ組み立てベンダに依存するため。Alliance 付属 のパッドライブラリ (padlib) を VDEC の要求に一致するように 修正する。

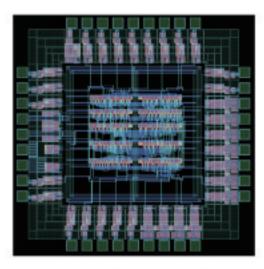

パッド組み立ての要求は、パッド間隔、チップ面積、パッド配 値位置がある。各パッドセルのレイアウトは、I/O パッファと電 源リング構成用の配線で構成されており、ring 実行後は、Fig. 9 のように配置される。そのため、使用した各セルのパッファ、電 源リングの幅を修正し、配置配線後に指定の位置にパッドを配置 する、パッドセルの修正例を Fig. 8(padlib) に示す。

Fig. 6 Layout design

Fig. 7 Pad library modification

## 6.4 設計上の問題点

#### 6.4.1 ポリシリコン上の Via 配置違反

デザインルールにおいて、ポリシリコン上に Via が存在する場合、その箇所のポリシリコンは Via の幅よりも広くとる必要があった。使用したセルライブラリのレイアウトでは、ポリシリコン上に Via を配置する箇所が存在したため、Via の配置位置を修正し、デザインルールエラーを解決した。

Fig. 8 Cells

Fig. 9 Chip Layout

#### 6.4.2 チップ規模増大

オンセミ 1.2µm プロセスはアルミ 2 層であり、アルミ 3 層以 上使用しオーバルーティングの Alliance Ver.5 ではなく、セル領 域外に配線領域を確保する Alliance Ver.4 を使用した。Ver.4 の 自動配線では、セル領域外に配線を確保するため、配線領域が増 えてしまうとチップ規模が大きくなってしまう。そのためチッ プ搭載可能な面積を越えてしまったため、縮小した回路を搭載 した。

#### 7. 考察

今までの各製造プロセスにおいて,発生した問題の改良を考察 する.過去のディーブサブミクロンプロセスと,今回試作したオ

Fig. 10 Routing

Fig. 11 Layout on Alliance dreal

| Process       | error                                   | provision                    |

|---------------|-----------------------------------------|------------------------------|

| Rohm 0.35pm   | Unconnected between segment and contact | Segment addition             |

| Rohm 0.18pm   | Spaced error by different layer         | Move the segment and contact |

|               | Unconnected between segment and contact | Segment addition             |

|               | clock skew                              | clock mesh                   |

| ON SEMI 1.2μm | Set Via over Poly                       | Move the ref                 |

|               | Scale expansion from tow-metals routing | Cut down on circuit          |

Table 3 errors

ンセミ 1.2 μm の試作の際に判明した、スケーラブルルールの問題点を Table 3 に示す。問題点のほとんどは、セルライブラリのセグメント、コンタクトの配置位置によるものであり、ライブラリの修正により対処が可能であるため、各製造プロセスにおいて共通となるスタンダードセルライブラリの作成は可能であると考えられる。また、2 層の配線方法においてもセル配置位置の改善により、搭載規模の縮小が見込める。

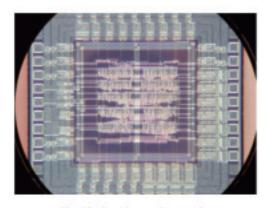

Fig. 12 Real layout photography

#### 8. まとめと課題

今回作成したチップ写真を Fig. 12 に示す。本研究では、ス ケーラブルなセルライブラリを用いた EDA ツールを用い、オン セミ  $1.2\mu m$  プロセスのチップ試作を行った。

結果、ディープサブミクロンプロセス、オンセミ 1.2μm の各 プロセスにおいて、同一のスタンダードセルライブラリをベース とし、若干の修正により、デザインルールエラーのないレイアウ トの設計が可能であることを実証した。

しかし、試作したチップは到着したばかりであるため、動作検証を行っていない。一連の試作によって、Alliance のスケーラブルルールの問題点が洗い出されてきたので、今後ディーブサブミクロンを含む多くのルールに対してスケーラブルとなるセルライブラリ、ならびに配置配線ツールを開発、試作したチップの実機テストが今後の課題である。

## 9. 謝辞

本研究は東京大学大規模集積システム設計教育研究センター を通し、日本ケイデンス株式会社の協力で行われたものである。

## 参考文献

- Alliance Home Page, http://www-asim.lip6.fr/recherche/alliance/.

- 2) VDEC Home Page, http://www.vdec.u-tokyo.ac.jp/.

- 3) 清水尚彦, SFL による LSI 設計入門, IP ARCH. Inc, 2003.

- 石黒健史, Alliance の Scalable CMOS Library によるチップ 試作の研究, 東海大学工学部卒業研究論文, 2003.

- 5) 飯田佳洋、システム LSI 統合開発環境の構築と同環境を用いたコンピュータシステムアーキテクチャ設計手法に関する研究、東海大学大学院修士論文、2004.

- 6) 飯田佳洋、清水尚彦、商用ソフトを用いない SFL ベースの LSI 開発、第24 回パルテノン研究会、2004.

- Takuya Higuchi, Jun'ichiro Ogane, Naohiko Shimizu, "Building A Design Flow for Deep Sub-micron Process(0.18um) with A Scalable Cell Library - Adjustment for Deep Submicron Process -", ITC-CSCC2010, 2010.

- Jun'ichiro Ogane, Hisayoshi Suehiro, Takuya Higuchi, Naohiko Shimizu, "Building A Design Flow for Deep Sub-micron Process(0.18um) with A Scalable Cell Library - A Solution Methodology of Clock Skew with Mesh-style Clock -", ITC-CSCC2010, 2010.

- Naohiko Shimizu, Masami Ikura, Warangrat Wiriya, Sorawat Chivapreecha, "A New Logic Circuit Design Methodology with UML", ITC-CSCC2009, 2009.