## 総合理工学研究科 Graduate School of Science and Technology 情報理工学コース Information Science and Technology

## Test method for VLSI

教授 浅川 毅

Professor

Takeshi ASAKAWA

Keyword: VLSI, Testing, Processor

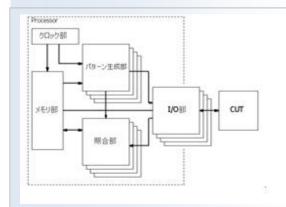

マイクロプロセッサやメモリに代表される VLSI は 半導体製造技術に伴い進化し続けている。そして 現在では多くの機能を実装し高速で動作する多品 種の VLSI が開発・製造されている。しかし、VLSI のテストでは全ての機能や構成要素をテストする 必要があるため、VLSI の複雑化はテスト時間の増 大を招き VLSI 製造コストを押し上げている現状に ある。この課題を解決するために我々は VLSI のテスト手法に関する研究を行っている。特に、VLSI に 印加するテストパターンや省電カテストの面に注 目している。昨年度は「機能テスト向け高速プロセッサのアーキテクチャ」を提案し、タイミングに関し て自由度の高いテストパターンを高速に生成する プロセッサを開発した。本年度はこの技術を発展さ せてタイミングテストや電流テストに対応する。

VLSI has become faster and more complex with advances semiconductor in manufacturing technology. However, there is a need for a very long time for LSI test for that reason. We are doing research on the test method of VLSI to solve this problem. particular, We are focused on low power consumption test and test pattern generation We propose the "architecture of method. functional testing for high-speed processor", then, we have developed a processor for implementing flexible timing at high speed. The next step is to adapt to the timing and current testing of these techniques.

◆リンクページ(Link): http://taraku.ec.u-tokai.ac.jp/

◆電子メール (address): asakawa@tokai.ac.jp