## 総合理工学研究科 Graduate School of Science and Technology 電気・電子コース Electrical and Electronics Engineering

## 多相クロックに基づくディジタル PLL の開発

Digital Phase-locked loop based on multi-phase clock

教授 矢原 充敏 Prof. Mitsutoshi YAHARA

Keyword: PLL・多相クロック・ディジタル回路

Topocs: Phase-Locked Loop・Multi-Phase Clock・

Digital Circuit

近年、モバイル通信機器の技術革新は目覚ましく、今後の IoT を支える重要なアイテムの一つです。そのモバイル通信機器内において、各システムを駆動させるクロック信号発生回路は、システムの安定性、低消費電力の面で重要な役割を担っています。

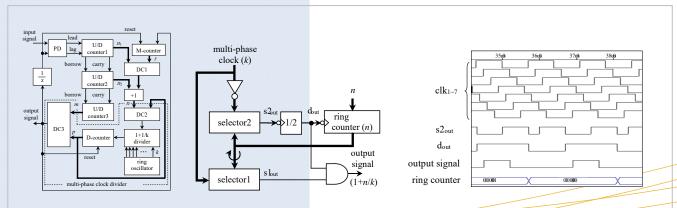

そのクロック信号発生回路として広く用いられている回路に位相同期ループ(PLL: Phase-Locked Loop)があります。PLL は、入力信号に位相が一致した信号を出力する回路であり、各システムのディジタル化に伴い、回路の集積化、安定性、信頼性等に対する要求から、全ディジタル構成による PLL(DPLL: Digital PLL)の研究が進められてきています。従来の DPLL では、ループを制御する基準クロックとして単相のクロックを使用していました。しかし、これでは制御がクロックの1周期単位となってしまい、ループの特性に大きな影響を与えていました。

本研究では、ループを制御する基準クロックとして多相のクロックを利用した新たな制御方式による DPLL の開発をおこない、諸特性の改善向上を目指します。これにより、今後の IoT の更なる発展に少しでも寄与していきたいと考えています。

In recent years, technological innovation of mobile communication equipment has been remarkable, it is one of the important items supporting the future IoT. In the mobile communication device, a clock signal generator for driving each system is an important role in the stability and low power consumption of the system.

There is a phase locked loop (PLL: Phase-Locked Loop) in a circuit widely used as its clock signal generator. The PLL is a circuit that outputs a signal whose phase matches the input signal. Along with the digitalization of each system, researches on PLL (DPLL: Digital PLL) based on all digital configurations has been conducted due to demand for circuit integration, stability, reliability and the like. In the conventional DPLL, a single phase clock was used as the reference clock for controlling the loop. However, in this case, since the control becomes one cycle unit of the clock, it affected the characteristics of the loop.

In this research, we develop a DPLL with a new control method that uses multi-phase clock as a reference clock for controlling loops, and aim to improve various characteristics. By doing so, I hope to contribute even a little to further development of IoT in the future.

DPLL based on multi-phase clock, 1+n/k frequency divider, and waveforms of 1+n/k frequency divider